# Übungen zur Grundlagen der Technischen Informatik Übung 12 – VHDL und Komparatoren

Florian Frank

Friedrich-Alexander-Universität Erlangen-Nürnberg

Wintersemester 2018/19

Organisatorisches: Vorlesungsevaluation

Organisatorisches: Vorlesungsevaluation

Aufgabe 1 – VHDL: Funktionen

Organisatorisches: Vorlesungsevaluation

Aufgabe 1 – VHDL: Funktionen

Aufgabe 2 – ALU in VHDL

Organisatorisches: Vorlesungsevaluation

Aufgabe 1 – VHDL: Funktionen

Aufgabe 2 – ALU in VHDL

Aufgabe 3 – VHDL: Automaten

Organisatorisches: Vorlesungsevaluation

Aufgabe 1 – VHDL: Funktionen

Aufgabe 2 – ALU in VHDL

Aufgabe 3 – VHDL: Automaten

Aufgabe 4 – Komparator

Organisatorisches: Vorlesungsevaluation

Aufgabe 1 – VHDL: Funktionen

Aufgabe 2 – ALU in VHDL

Aufgabe 3 – VHDL: Automaten

Aufgabe 4 – Komparator

Korrektur und Besprechung der ersten Miniklausur

# Organisatorisches: Vorlesungsevaluation

# **Aufgabe 1 – VHDL: Funktionen**

### Aufgabe 1 – VHDL: Funktionen

Im VHDL-2008-Standard wurde ein unärer or-Operator eingeführt, der die Elemente eines beliebig langen Vektors vom Typ std\_logic\_vector mittels sukzessiver Veroderung auf eine 1 Bit lange Ausgabe vom Typ std\_logic reduziert.

Entwickeln Sie eine Funktion or\_reduce, die dieselbe Semantik hat wie der beschriebene Operator, um auch Werkzeuge zu unterstützen, die den Standard noch nicht implementieren. Verwenden Sie dazu eine for-Schleife und erläutern Sie, wie sich deren Semantik von Schleifen in Software-Programmiersprachen unterscheidet.

Mit VHDL "programmieren" wir unsere Hardware und das auf einem möglichst hohen Abstraktionsniveau.

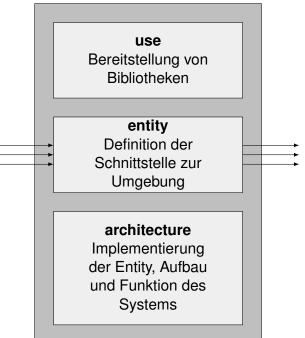

In der Darstellung rechts ist der allgemeine Aufbau einer VHDL-Beschreibung dargestellt.

use IEEE.std\_logic\_1164.all; -- Inkludiert das

Paket std\_logic\_1164 aus der Bibliothek IEEE

Mit VHDL "programmieren" wir unsere Hardware und das auf einem möglichst hohen Abstraktionsniveau. In der Darstellung rechts ist der allgemeine Aufbau einer VHDL-Beschreibung dargestellt.

### use – Bereitstellung von Bibliotheken

- Genauso wie in Java, gibt es auch in VHDL Pakete, in denen verschiedene Typen oder Funktionen definiert sind (zum Beispiel der Typ std\_logic aus der IEEE-Bibliothek).

- Diese werden dann über den use-Befehl "importiert". Am Beispiel:

```

1 use IEEE.std_logic_1164.all; -- Inkludiert das

Paket std_logic_1164 aus der Bibliothek IEEE

```

Mit VHDL "programmieren" wir unsere Hardware und das auf einem möglichst hohen Abstraktionsniveau.

In der Darstellung rechts ist der allgemeine Aufbau einer VHDL-Beschreibung dargestellt.

### entity – Definition einer Schnittstelle

Eine "Entität" beschreibt die "black-box" einer Komponente. Sie besteht nur aus den **Ein-** sowie Ausgängen derselbigen.

```

entity entity_name is

port (

port_list -- hier stehen Ein- und Ausgaenge

);

end [entity_name];

```

Mit VHDL "programmieren" wir unsere Hardware und das auf einem möglichst hohen Abstraktionsniveau.

In der Darstellung rechts ist der allgemeine Aufbau einer VHDL-Beschreibung dargestellt.

### architecture - Implementierung

Die "Architektur" einer Entität beschreibt nun den inneren Aufbau, sowie die Funktionalität derselbigen.

```

architecture architecture_name of entity_name is

-- hier stehen nur intern genutzte Signale

begin

-- hier steht, was die Entitaet macht

end [architecture] architecture_name;

```

# VHDL: VHSIC Hardware Description Language (II) – Grundlegendes

#### Kommentare

```

1 -- Ein Kommentar muss immer mit einem doppelten Minus (--) beginnen und geht bis

zum Ende der Zeile

2 Hier ist kein Kommentar

3 -- Hier schon

```

#### Bezeichner

Bezeichner sind in VHDL case-insensitive (sprich: Groß- und Kleinschreibung werden nicht unterschieden). Sie **müssen** mit einem Buchstaben anfangen, anschließend können Buchstaben, Zahlen oder Unterstriche folgen. Zwei Unterstriche dürfen sich dabei **nicht** unmittelbar folgen.

### **Reservierte Wörter**

| after                                | else                                 | library                      | port      | sll        |

|--------------------------------------|--------------------------------------|------------------------------|-----------|------------|

| alias                                | elsif                                | linkage                      | postponed | sra        |

| all                                  | end                                  | literal                      | procedure | srl        |

| and                                  | entity                               | loop                         | process   | subtype    |

| architecture                         | exit                                 | map                          | pure      | then       |

| array                                | file                                 | mod                          | range     | to         |

| assert                               | for                                  | nand                         | record    | transport  |

| attribute                            | function                             | new                          | register  | type       |

| begin                                | generate                             | next                         | reject    | unaffected |

| block                                | generic                              | nor                          | rem       | units      |

| body                                 | group                                | not                          | report    | until      |

| buffer                               | guarded                              | null                         | return    | use        |

| bus                                  | if                                   | of                           | rol       | variable   |

| case                                 | impure                               | on                           | ror       | wait       |

| component                            | in                                   | open                         | select    | when       |

| configuration                        | inertial                             | or                           | severity  | while      |

| constant                             | inout                                | others                       | signal    | with       |

| disconnect                           | is                                   | out                          | shared    | xnor       |

| downto<br>WS 2018/19   Florian Frank | FAU abel   DeGTI - Übung 12: VHDL ur | package<br>nd komparatoreige | sla       | xor        |

# VHDL: VHSIC Hardware Description Language (II) – Grundlegendes

#### Variablen

Genauso wie in Java oder C, enthält eine Variable in VHDL nur eine Information: den aktuellen Wert.

```

variable v1 : std_logic; -- Variablendeklaration

v1 := 1; -- Wertzuweisung

```

#### Konstanten

Konstanten verhalten sich ähnlich zu Variablen mit dem Unterschied, dass sie nicht verändert werden können.

```

constant c1 : std_logic := X; -- Konstantendeklaration

```

### Signale

Signale und Variablen sind ähnlich, es gibt aber einige Unterschiede bei der Verwendung der beiden.

```

signal s1 : std_logic; -- Signaldeklaration

s1 <= X; -- Wertzuweisung

```

# VHDL: VHSIC Hardware Description Language (II) – Grundlegendes

#### Variablen

Genauso wie in Java oder C, enthält eine Variable in VHDL nur eine Information: den aktuellen Wert Variablen verhalten sich insbesondere gleich dem Programmiersprachenkonstrukt, als dass sie **sequentiell** genutzt werden und **überschreibbar** sind.

### ■ Konstanten

Konstanten verhalten sich ähnlich zu Variablen mit dem Unterschied, dass sie nicht verändert werden können.

```

constant c1 : std_logic := X; -- Konstantendeklaration

```

### Signale

Signale und Variablen sind ähnlich, es gibt aber einige Unterschiede bei der Verwendung der beiden.

Signale sind vorzustellen als verdrahtete Leitungen, was ihre **nebenläufige** Natur begründet. Ihnen kann in einem Abschnitt nicht mehrfach Werte zugewiesen werden, der zuletzt zugewiesene Wert gilt.

# VHDL: VHSIC Hardware Description Language (II) – Beispiel

Welchen Wert enthalten  $s_2$  und  $v_2$  am Ende der Prozedur?

```

procedure p wertezuweisung (

variable v1 : integer;

variable v2 : integer;

signal s1 : out integer := 5;

signal s2 : out integer

) is

begin

for I in 1 to 10 loop

v1 \ll I;

s1 <= I;

10

end loop;

11

v2 <= v1;

s2 <= s1;

13

14 end p_wertezuweisung;

```

# VHDL: VHSIC Hardware Description Language (II) – Beispiel

Welchen Wert enthalten  $s_2$  und  $v_2$  am Ende der Prozedur?

```

procedure p wertezuweisung (

variable v1 : integer;

variable v2 : integer;

signal s1 : out integer := 5;

signal s2 : out integer

) is

begin

for I in 1 to 10 loop

v1 \leftarrow I;

s1 <= I;

10

end loop;

11

v2 <= v1;

s2 <= s1;

13

14 end p_wertezuweisung;

```

$v_2$  enthält den Wert 10,  $s_2$  aber 5.

#### ■ Funktionen

Funktionen stellen ein *sequentielles* Unterprogramm mit Rückgabewert dar und können auch rekursiv aufgerufen werden. Sie dürfen ihre Parameter **nicht** verändern.

```

function identifier [ ( formal parameter list ) ] return a_type is

[ declarations, see allowed list below ]

begin

sequential statement(s)

return some_value; -- muss vom Typ a_type sein

end function identifier;

```

Die Elemente der "formal parameter list" werden durch ein Semikolon (;) von einander getrennt, dem letzten folgt aber **keines**. Ebenfalls darf kein Parameter vom Modus **inout** oder **out** sein.

Erlaubte Deklarationen enthalten unter anderem ...

- □ ... die Deklaration und der Körper eines Unterprogramms

- □ ... Konstanten □ ... Variablen □ ... Typen und Subtypen

... aber **nicht** die Deklaration von Signalen.

#### Prozeduren

Prozeduren stellen ein *sequentielles* Unterprogramm ohne Rückgabewert dar. Sie geben Werte zurück, indem sie ihre Parameter oder globale Objekte verändern.

```

procedure identifier [ ( formal parameter list ) ] is

[ declarations, see allowed list below ]

begin

sequential statement(s)

end procedure identifier;

```

Die Elemente der "formal parameter list" werden durch ein Semikolon (;) von einander getrennt, dem letzten folgt aber **keines**.

Erlaubte Deklarationen enthalten unter anderem ...

- □ ... die Deklaration und der Körper eines Unterprogramms

- ... Konstanten

- □ ... Typen und Subtypen

- ... aber **nicht** die Deklaration von Signalen.

```

1 library ieee;

2 use ieee.std logic 1164.all;

3 use ieee.numeric std.all;

-- Purpose: This function performs a bitwise xor on the input vector

function f BITWISE XOR (

r SLV IN : in std logic vector

) return std logic is

variable v XOR : std logic := '0';

10 begin

for i in 0 to r_SLV_IN'length-1 loop

11

v XOR := v XOR xor r SLV IN(i);

12

end loop;

13

return v XOR;

15 end function f BITWISE XOR;

```

#### Prozeduren

Prozeduren stellen ein *sequentielles* Unterprogramm ohne Rückgabewert dar. Sie geben Werte zurück, indem sie ihre Parameter oder globale Objekte verändern.

```

procedure identifier [ ( formal parameter list ) ] is

[ declarations, see allowed list below ]

begin

sequential statement(s)

end procedure identifier;

```

Die Elemente der "formal parameter list" werden durch ein Semikolon (;) von einander getrennt, dem letzten folgt aber **keines**.

Erlaubte Deklarationen enthalten unter anderem ...

- □ ... die Deklaration und der Körper eines Unterprogramms

- □ ... Konstanten

- □ ... Typen und Subtypen

- ... aber **nicht** die Deklaration von Signalen.

Prozedur-/Funktionaufruf Ruft eine Prozedur oder Funktion auf.

```

[ label: ] procedure-name [ ( actual parameters ) ] ;

```

### ■ if-Abfragen

```

[ label: ] if condition1 then

sequence-of-statements

selsif condition2 then \_ optional

sequence-of-statements /

elsif condition3 then \_ optional

sequence-of-statements /

...

else \_ optional

sequence-of-statements /

optional

sequence-of-statements /

end if [ label ] ;

```

#### switch-case

Führt aufgrund einer gewissen Wahl einen spezifischen Fall aus. Wahlmöglichkeiten müssen Konstanten desselben diskreten Typen wie der Ausdruck sein.

#### Schleifen

Wiederholte Ausfürhung von Code, kommt in dreierlei verschiedenen Ausführungen.

```

[ label: ] loop

sequence-of-statements -- use exit statement to get out

end loop [ label ] ;

[ label: ] for variable in range loop

sequence-of-statements

end loop [ label ] ;

[ label: ] while condition loop

sequence-of-statements

end loop [ label ] ;

```

#### next

Das continue von VHDL, kann auch gleichzeitig noch Bedingung für Fortsetzung enthalten.

```

[ label: ] next [ label2 ] [ when condition ] ;

```

#### exit

Das break von VHDL, kann auch gleichzeitig noch Bedingung für "Ausbruch" enthalten.

```

[ label: ] exit [ label2 ] [ when condition ] ;

```

#### ■ return

Gibt einen Wert in Funktionen zurück.

```

[ label: ] return [ expression ] ;

```

### ■ null

Wird ein "Statement" gebraucht, man will nichts tun, so hilft null im nun.

```

1 null ;

```

# Aufgabe 1 – VHDL: Funktionen, Lösung der Aufgabe

```

function or_reduce(arg: std_logic_vector) return std_logic is

variable result : std_logic;

begin

result := '0';

for i in arg'range loop

result := result or arg(i);

end loop;

return result;

end or_reduce;

```

Die Ähnlichkeit zu Software-Programmiersprachen trügt:

Wird or\_reduce in zu synthetisierendem Code (das heißt in tatsächlichen Hardware-Designs und nicht der Simulation) verwendet, wird die Schleife nicht sequentiell realisiert. Stattdessen werden für jede Iteration Hardware-Komponenten inferriert (im einfachsten, unoptimierten Fall hier zum Beispiel schlicht arg'high Oder-Gatter). Dies ist auch der Grund, wieso in synthetisierbarem VHDL-Code die Schleifengrenzen zur Übersetzungszeit bekannt sein müssen.

# Aufgabe 2 – ALU in VHDL

### Aufgabe 2 – ALU in VHDL

Entwerfen Sie ein Rechenwerk alu (*Arithmetic Logic Unit*), das in Abhängigkeit eines Steuersignals *op* auf zwei 8 Bit lange Eingabevektoren *a* und *b* die folgenden Operationen durchführt und das Ergebnis auf dem ebenfalls 8 Bit langen Ausgabevektor *result* ausgibt:

- $result \leftarrow a + b$  falls op = 00

- $result \leftarrow a b$  falls op = 01

- $result \leftarrow a \land b$  falls op = 10

- $result \leftarrow a \cdot 2$  (um 1 Linksschieben) falls op = 11

Verwenden Sie Signale des Typs std\_logic\_vector für die Schnittstelle und die in der IEEE-Bibliothek numeric\_std definierten Operationen für die Berechnungen.

### Zuerst müssen die benötigten Bibliotheken eingebunden werden:

```

library ieee;

use ieee.std_logic_1164.all; -- std_logic_vector

use ieee.numeric_std.all; -- fuer Arithmetik

```

Zuerst müssen die benötigten Bibliotheken eingebunden werden:

```

library ieee;

use ieee.std_logic_1164.all; -- std_logic_vector

use ieee.numeric_std.all; -- fuer Arithmetik

```

Anschließend wird die zu entwerfende entity beschrieben mit ihren Einund Ausgängen. Für die ALU benötigen wir die beiden Operanden *a* und *b* sowie die auszuführende Operation *op* als Eingänge und das Ergebnis *result* als Ausgang:

Als nächstes folgt die eigentliche Implementierung der entity<sup>1</sup>, innerhalb einer architecture. Zu Beginn der architecture müssen zunächst alle internen Signale deklariert werden.

```

architecture behavioral of alu is

signal signed_result : signed(8 downto 0);

signal integer_b : integer;

```

<sup>&</sup>lt;sup>1</sup>Eine entity kann mehrere architectures haben.

Als nächstes folgt die eigentliche Implementierung der entity<sup>1</sup>, innerhalb einer architecture. Zu Beginn der architecture müssen zunächst alle internen Signale deklariert werden.

```

architecture behavioral of alu is

signal signed_result : signed(8 downto 0);

signal integer_b : integer;

```

Schließlich beschreiben wir das Verhalten der architecture. Der s11-Operator (Linksschieben) benötigt einen zweiten Operanden vom Typ integer, weshalb wir ein Hilfssignal integer\_b verwenden. Dem Compiler muss bei der Umwandlung in einen integer mitgeteilt werden, ob der Bitvektor *b* vorzeichenbehaftet interpretiert werden soll oder nicht, weshalb zwei Typwandlungen notwendig sind:

```

begin

integer_b <= to_integer(signed(b));</pre>

```

<sup>&</sup>lt;sup>1</sup>Eine entity kann mehrere architectures haben.

Nun folgen die eigentliche durchzuführende Operation, welche wir kombinatorisch implementieren und somit keinen process benötigen.

Nun folgen die eigentliche durchzuführende Operation, welche wir kombinatorisch implementieren und somit keinen process benötigen. Die arithmetischen Bitoperationen aus numeric\_std sind für vorzeichenbehaftete und nicht vorzeichenbehaftete Operanden unterschiedlich überladen, weshalb wir, falls nötig, die geforderte Typumwandlung vornehmen:

Nun folgen die eigentliche durchzuführende Operation, welche wir kombinatorisch implementieren und somit keinen process benötigen. Die arithmetischen Bitoperationen aus numeric\_std sind für vorzeichenbehaftete und nicht vorzeichenbehaftete Operanden unterschiedlich überladen, weshalb wir, falls nötig, die geforderte Typumwandlung vornehmen:

```

with op select signed_result <=

(signed(a) + signed(b)) when "00",

(signed(a) - signed(b)) when "01",

signed(a and b) when "10",

signed(a sll 1) when "11",

"000000000" when others;</pre>

```

```

with op select signed_result <=

(signed(a) + signed(b)) when "00",

(signed(a) - signed(b)) when "01",

signed(a and b) when "10",

signed(a sll 1) when "11",

"000000000" when others;</pre>

```

Das with signal select-Konstrukt inferriert einen Multiplexer, der zwischen den vier Ergebnissen auswählt. Entsprechend werden alle vier möglichen Operationen gleichzeitig berechnet.

```

with op select signed_result <=

(signed(a) + signed(b)) when "00",

(signed(a) - signed(b)) when "01",

signed(a and b) when "10",

signed(a sll 1) when "11",

"000000000" when others;</pre>

```

Das with signal select-Konstrukt inferriert einen Multiplexer, der zwischen den vier Ergebnissen auswählt. Entsprechend werden alle vier möglichen Operationen gleichzeitig berechnet. Zuletzt muss das Ergebnis zurück in einen std\_logic\_vector umgewandelt und dem Ausgangs-port zugewiesen werden:

```

with op select signed_result <=

(signed(a) + signed(b)) when "00",

(signed(a) - signed(b)) when "01",

signed(a and b) when "10",

signed(a sll 1) when "11",

"000000000" when others;</pre>

```

Das with signal select-Konstrukt inferriert einen Multiplexer, der zwischen den vier Ergebnissen auswählt. Entsprechend werden alle vier möglichen Operationen gleichzeitig berechnet. Zuletzt muss das Ergebnis zurück in einen std\_logic\_vector umgewandelt und dem Ausgangs-port zugewiesen werden:

```

result <= std_logic_vector(signed_result)(7 downto 0);

end architecture;</pre>

```

```

1 library ieee;

2 use ieee.std logic 1164.all; -- std logic vector

3 use ieee.numeric std.all; -- fuer Arithmetik

entity alu is

port(

6

a, b : in std logic vector(7 downto 0);

op : in std logic vector(1 downto 0);

8

result : out std logic vector(7 downto 0)

9

);

10

11 end entity alu;

12

13 architecture behavioral of alu is

signal signed_result : signed(8 downto 0);

14

signal integer_b : integer;

16 begin

integer b <= to integer(signed(b));</pre>

17

18

with op select signed result <=</pre>

19

(signed(a) + signed(b)) when "00",

20

(signed(a) - signed(b)) when "01",

21

signed(a and b) when "10",

22

signed(a sll 1) when "11",

"00000000" when others;

24

result <= std logic vector(signed result)(7 downto 0);

26 end architecture;

```

# **Aufgabe 3 – VHDL: Automaten**

### Aufgabe 3 – VHDL: Automaten

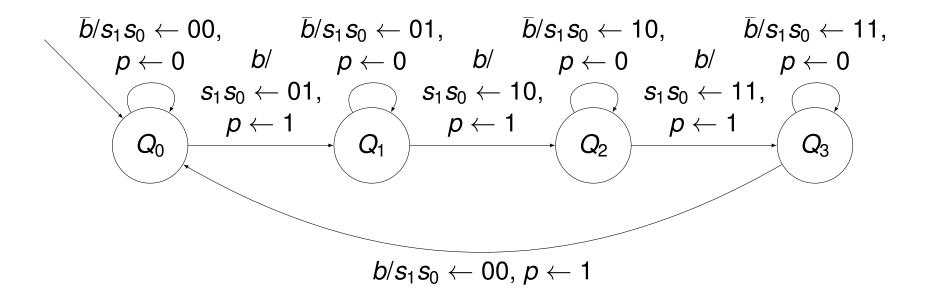

Implementieren Sie den folgenden Mealy-Automaten, der die Armbanduhr aus Übung 11 beschreibt, in VHDL. Der Automat soll mit einem synchronen Reset-Signal in den Anfangszustand zurückgesetzt werden können.

a) Entwickeln Sie einen 1-Bit-Komparator, der zwei Bits a und b miteinander vergleicht und auf den Ausgängen <, > und = die Gültigkeit der drei Relationen a < b, a > b und a = b ausgibt (1 entspreche wahr). Achten Sie darauf, dass stets genau einer der drei Ausgänge aktiv ist.

b) Entwerfen Sie nun eine digitale Schaltung, deren Eingänge die Ausgänge  $K_0 = (<_0, >_0, =_0)$  und  $K_1 = (<_1, >_1, =_1)$  zweier Komparatoren sind und die diese *lexikographisch* auf die Ausgabe (<, >, =) reduziert. Dabei soll  $K_0$  nieder- und  $K_1$  höherwertig sein.

#### Lexikographisch

Gegeben sei ein quasigeordnetes Alphabet  $(\Sigma, \leq)$ , d. i. eine Menge von Zeichen  $a_i, b_j \in \Sigma$ . Eine Zeichenkette  $a = (a_1, a_2, \ldots)$  ist lexikographisch kleiner als eine Zeichenkette  $b = (b_1, b_2, \ldots)$ , das heißt a liegt in der Sortierung vor b, wenn beim komponentenweisen Vergleich Zeichen für Zeichen ...

#### Lexikographisch

Gegeben sei ein quasigeordnetes Alphabet  $(\Sigma, \leq)$ , d. i. eine Menge von Zeichen  $a_i, b_j \in \Sigma$ . Eine Zeichenkette  $a = (a_1, a_2, \ldots)$  ist lexikographisch kleiner als eine Zeichenkette  $b = (b_1, b_2, \ldots)$ , das heißt a liegt in der Sortierung vor b, wenn beim komponentenweisen Vergleich Zeichen für Zeichen ...

1. das Zeichen  $a_i$  von a mit dem niedrigsten Index i, in dem sich die beiden Zeichenketten unterscheiden, (echt) kleiner ist als das entsprechende Zeichen  $b_i$  von b,

#### Lexikographisch

Gegeben sei ein quasigeordnetes Alphabet  $(\Sigma, \leq)$ , d. i. eine Menge von Zeichen  $a_i, b_j \in \Sigma$ . Eine Zeichenkette  $a = (a_1, a_2, \ldots)$  ist lexikographisch kleiner als eine Zeichenkette  $b = (b_1, b_2, \ldots)$ , das heißt a liegt in der Sortierung vor b, wenn beim komponentenweisen Vergleich Zeichen für Zeichen ...

1.

$$a_i \leq b_i \wedge b_i \not\leq a_i$$

,

#### Lexikographisch

Gegeben sei ein quasigeordnetes Alphabet  $(\Sigma, \leq)$ , d. i. eine Menge von Zeichen  $a_i, b_j \in \Sigma$ . Eine Zeichenkette  $a = (a_1, a_2, \ldots)$  ist lexikographisch kleiner als eine Zeichenkette  $b = (b_1, b_2, \ldots)$ , das heißt a liegt in der Sortierung vor b, wenn beim komponentenweisen Vergleich Zeichen für Zeichen ...

- 1.  $a_i \leq b_i \wedge b_i \not\leq a_i$ ,

- 2. oder wenn a ein Präfix von b (d. h.  $a_i \le b_i \land b_i \le a_i$  für alle verfügbaren i), aber kürzer ist.

#### Lexikographisch bei Wörtern mit festen Längen

Gegeben sei ein quasigeordnetes Alphabet  $(\Sigma, \leq)$ , d. i. eine Menge von Zeichen  $a_i, b_j \in \Sigma$ . Ein geordnetes Paar  $(a_1, a_2) \in \Sigma^2$  ist *lexikographisch kleiner* als ein geordnetes Paar  $(b_1, b_2) \in \Sigma^2$ , wenn ...

- 1.  $a_1 < b_1$  oder

- 2.  $a_1 = b_1$  und  $a_2 < b_2$

c) Betrachten Sie schließlich die in a) und b) entworfenen Schaltungen jeweils als Blackbox mit den gegebenen Schaltsymbolen. Entwerfen Sie ausschließlich mit diesen Komponenten einen Komparator für vorzeichenlose 4-Bit-Binärzahlen. Welche Möglichkeiten gibt es, die Komponenten zusammenzuschalten, und welche Auswirkungen hat dies auf die benötigte Fläche und den kritischen Pfad?

# Korrektur und Besprechung der ersten Miniklausur